Lesson 09: Behavioral Modeling

Behavioral modeling in Verilog is used to describe a digital circuit using logic expression and C-like constructs. Behavioral modeling allows for the description of circuits based on their function rather than their hardware components. Usually, it describes how the outputs are computed as functions of the inputs.

In Behavioral modeling, the data assignments are not carried out continuously instead they happened on specific events specified in the sensitivity list. This type of modeling scheme is implemented using procedural blocks. All procedures in Verilog are specified within one of the following four blocks:

- always block

- initial block

- task

- function

Tasks and functions are procedures that are enabled from one or more places in other procedures. Tasks and functions are covered in "EE2440-FPGA Lab 12: Finite State Machine (Mealy State Machine)".

The initial and always statements are enabled at the beginning of the simulation. The initial statement executes only once and its activity dies when the statement has finished. The always statement executes repeatedly. Its activity dies only when the simulation is terminated. They can be compared to the setup() and loop() functions in the Arduino C respectively. There is no limit to the number of initial and always blocks that can be defined in a module.

Also, the output variables must be declared as reg because they need to keep hold of the previous value until a new assignment occurs after any change in the specified sensitivity list.

initial Procedure

An "initial" statement is executed only once in simulation.

The syntax for the initial block is as follows:

initial [timing_control] procedural_statement;

initial [timing_control] begin

multiple_procedural_statements;

end

The initial statement is non-synthesizable and is normally used in test benches to generate inputs at the desired time to test the module.

always procedure

Each "always" statement repeats continuously throughout the whole simulation run and circuit execution.

The syntax for the always block is as follows:

always @ (<sensitive List>) procedural_statement;

always @ (<sensitive List>) begin

multiple_procedural_statements;

end

The always statement is synthesizable, and the resulting circuit can be a combinatorial or sequential circuit.

In order for the model to generate a combinatorial circuit, the always block must meet all the following requirements:

- It should not be edge sensitive.

- Every branch of the conditional statement should define all output.

- Every case of case statement should define all output and must have a default case.

To generate a sequential circuit, the always block has the following functions:

- It should be trigger on edges: posedge and/or negedge. (positive edge or Negative edge)

Assignments

Procedural assignments occur within procedures such as always, initial, task, and functions and are used to place values onto variables. The variable will hold the value until the next assignment to the same variable.

Questions

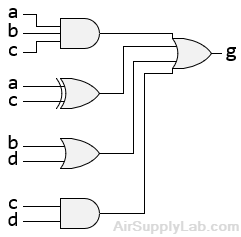

- Use behavioral modeling to describe the circuit in the following figure.