Lesson 10: GPIO Port Control Register (GPIOPCTL)

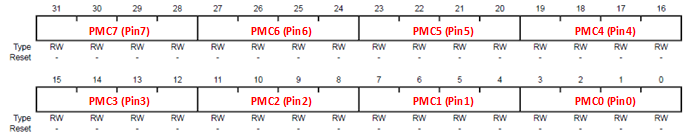

The GPIOPCTL register is used in conjunction with the GPIOAFSEL register and selects the specific peripheral signal for each GPIO pin when using the alternate function mode. Most bits in the GPIOAFSEL register are cleared on reset, therefore most GPIO pins are configured as GPIOs by default. When a bit is set in the GPIOAFSEL register, the corresponding GPIO signal is controlled by an associated peripheral. The GPIOPCTL register selects one out of a set of peripheral functions for each GPIO, providing additional flexibility in signal definition. Following tables are the information on the defined encodings for the bit fields in this register.

TM4C123G MCU

| I/O | Analog Function |

Digital Function (GPIOx->PCTL PMCn Field Encoding) | |||||||||||||||

| 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF | ||

| 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 | ||

| PA0 | — | GPIO | U0Rx | — | — | — | — | — | — | CAN1Rx | — | — | — | — | — | — | — |

| PA1 | — | GPIO | U0Tx | — | — | — | — | — | — | CAN1Tx | — | — | — | — | — | — | — |

| PA2 | — | GPIO | — | SSI0CLK | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PA3 | — | GPIO | — | SSI0Fss | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PA4 | — | GPIO | — | SSI0Rx | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PA5 | — | GPIO | — | SSI0Tx | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PA6 | — | GPIO | — | — | I2C1SCL | — | M1PWM2 | — | — | — | — | — | — | — | — | — | — |

| PA7 | — | GPIO | — | — | I2C1SDA | — | M1PWM3 | — | — | — | — | — | — | — | — | — | — |

| PB0 | USB0ID | GPIO | U1Rx | — | — | — | — | — | T2CCP0 | — | — | — | — | — | — | — | — |

| PB1 | USB0VBUS | GPIO | U1Tx | — | — | — | — | — | T2CCP1 | — | — | — | — | — | — | — | — |

| PB2 | — | GPIO | — | — | I2C0SCL | — | — | — | T3CCP0 | — | — | — | — | — | — | — | — |

| PB3 | — | GPIO | — | — | I2C0SDA | — | — | — | T3CCP1 | — | — | — | — | — | — | — | — |

| PB4 | AIN10 | GPIO | — | SSI2Clk | — | M0PWM2 | — | — | T1CCP0 | CAN0Rx | — | — | — | — | — | — | — |

| PB5 | AIN11 | GPIO | — | SSI2Fss | — | M0PWM3 | — | — | T1CCP1 | CAN0Tx | — | — | — | — | — | — | — |

| PB6 | — | GPIO | — | SSI2Rx | — | M0PWM0 | — | — | T0CCP0 | — | — | — | — | — | — | — | — |

| PB7 | — | GPIO | — | SSI2Tx | — | M0PWM1 | — | — | T0CCP1 | — | — | — | — | — | — | — | — |

| PC0 | — | GPIO | TCK SWCLK |

— | — | — | — | — | T4CCP0 | — | — | — | — | — | — | — | — |

| PC1 | — | GPIO | TMS SWDIO |

— | — | — | — | — | T4CCP1 | — | — | — | — | — | — | — | — |

| PC2 | — | GPIO | TDI | — | — | — | — | — | T5CCP0 | — | — | — | — | — | — | — | — |

| PC3 | — | GPIO | TDO SWO |

— | — | — | — | — | T5CCP1 | — | — | — | — | — | — | — | — |

| PC4 | C1- | GPIO | U4Rx | U1Rx | — | M0PWM6 | — | IDX1 | WT0CCP0 | U1RTS | — | — | — | — | — | — | — |

| PC5 | C1+ | GPIO | U4Tx | U1Tx | — | M0PWM7 | — | PhA1 | WT0CCP1 | U1CTS | — | — | — | — | — | — | — |

| PC6 | C0+ | GPIO | U3Rx | — | — | — | — | PhB1 | WT1CCP0 | USB0EPEN | — | — | — | — | — | — | — |

| PC7 | C0- | GPIO | U3Tx | — | — | — | — | — | WT1CCP1 | USB0PFLT | — | — | — | — | — | — | — |

| PD0 | AIN7 | GPIO | SSI3Clk | SSI1Clk | I2C3SCL | M0PWM6 | M1PWM0 | — | WT2CCP0 | — | — | — | — | — | — | — | — |

| PD1 | AIN6 | GPIO | SSI3Fss | SSI1Fss | I2C3SDA | M0PWM7 | M1PWM1 | — | WT2CCP1 | — | — | — | — | — | — | — | — |

| PD2 | AIN5 | GPIO | SSI3Rx | SSI1Rx | — | M0FAILT0 | — | — | WT3CCP0 | USB0EPEN | — | — | — | — | — | — | — |

| PD3 | AIN4 | GPIO | SSI3Tx | SSI1Tx | — | — | — | IDX0 | WT3CCP1 | USB0PFLT | — | — | — | — | — | — | — |

| PD4 | USB0DM | GPIO | U6Rx | — | — | — | — | — | WT4CCP0 | — | — | — | — | — | — | — | — |

| PD5 | USB0DP | GPIO | U6Tx | — | — | — | — | — | WT4CCP1 | — | — | — | — | — | — | — | — |

| PD6 | — | GPIO | U2Rx | — | — | M0FAULT0 | — | PhA0 | WT5CCP0 | — | — | — | — | — | — | — | — |

| PD7 | — | GPIO | U2Tx | — | — | — | — | PhB0 | WT5CCP1 | NMI | — | — | — | — | — | — | — |

| PE0 | AIN3 | GPIO | U7Rx | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE1 | AIN2 | GPIO | U7Tx | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE2 | AIN1 | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE3 | AIN0 | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE4 | AIN9 | GPIO | U5Rx | — | I2C2SCL | M0PWM4 | M1PWM2 | — | — | CAN0Rx | — | — | — | — | — | — | — |

| PE5 | AIN8 | GPIO | U5Tx | — | I2C3SDA | M0PWM5 | M1PWM3 | — | — | CAN0TX | — | — | — | — | — | — | — |

| PF0 | — | GPIO | U1RTS | SSI1Rx | CAN0Rx | — | M1PWM4 | PhA0 | T0CCP0 | NMI | C0o | — | — | — | — | — | — |

| PF1 | — | GPIO | U1CTS | SSI1Tx | — | — | M1PWM5 | PhB0 | T0CCP1 | — | C1o | — | — | — | — | TRD1 | — |

| PF2 | — | GPIO | — | SSI1Clk | — | M0FAULT0 | M1PWM6 | — | T1CCP0 | — | — | — | — | — | — | TRD0 | — |

| PF3 | — | GPIO | — | SSI1Fss | CAN0Tx | — | M1PWM7 | — | T1CCP1 | — | — | — | — | — | — | TRCLK | — |

| PF4 | — | GPIO | — | — | — | — | M1FAULT0 | IDX0 | T2CCP0 | USB0EPEN | — | — | — | — | — | — | — |

| I/O | Analog Function |

0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF | ||

| Digital Function (GPIOx->PCTL PMCn Field Encoding) | |||||||||||||||||

PD7 and PF0 are configured as GPIO by default but is locked and can only be reprogrammed by unlocking the pin in the GPIOLOCK register and uncommitting it by setting the GPIOCR register.

TM4C1294 MCU

| I/O | Analog Function |

Digital Function (GPIOx->PCTL PMCn Field Encoding) | |||||||||||||||

| 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF | ||

| 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 | ||

| PA0 | — | GPIO | U0Rx | I2C9SCL | T0CCP0 | — | — | — | CAN0Rx | — | — | — | — | — | — | — | — |

| PA1 | — | GPIO | U0Tx | I2C9SDA | T0CCP1 | — | — | — | CAN0Tx | — | — | — | — | — | — | — | — |

| PA2 | — | GPIO | U4Rx | I2C8SCL | T1CCP0 | — | — | — | — | — | — | — | — | — | — | — | SSI0CLK |

| PA3 | — | GPIO | U4Tx | I2C8SDA | T1CCP1 | — | — | — | — | — | — | — | — | — | — | — | SSI0Fss |

| PA4 | — | GPIO | U3Rx | I2C7SCL | T2CCP0 | — | — | — | — | — | — | — | — | — | — | — | SSI0XDAT0 |

| PA5 | — | GPIO | U3Tx | I2C7SDA | T2CCP1 | — | — | — | — | — | — | — | — | — | — | — | SSI0XDAT1 |

| PA6 | — | GPIO | U2Rx | I2C6SCL | T3CCP0 | — | USB0EPEN | — | — | — | — | — | — | — | SSI0XDAT2 | — | EPI0S8 |

| PA7 | — | GPIO | U2Tx | I2C6SDA | T3CCP1 | — | USB0PFLT | — | — | — | — | — | USB0EPEN | — | SSI0XDA3 | — | EPI0S9 |

| PB0 | USB0ID | GPIO | U1Rx | I2C5SCL | T4CCP0 | — | — | — | CAN1Rx | — | — | — | — | — | — | — | — |

| PB1 | USB0VBUS | GPIO | U1Tx | I2C5SDA | T4CCP1 | — | — | — | CAN1Tx | — | — | — | — | — | — | — | — |

| PB2 | — | GPIO | — | I2C0SCL | T5CCP0 | — | — | — | — | — | — | — | — | — | — | USB0STP | EPI0S27 |

| PB3 | — | GPIO | — | I2C0SDA | T5CCP1 | — | — | — | — | — | — | — | — | — | — | USB0CLK | EPI0S28 |

| PB4 | AIN10 | GPIO | U0CTS | I2C5SCL | — | — | — | — | — | — | — | — | — | — | — | — | SSI1Fss |

| PB5 | AIN11 | GPIO | U0RTS | I2C5SDA | — | — | — | — | — | — | — | — | — | — | — | — | SSI1Clk |

| PC0 | — | GPIO | TCK SWCLK |

— | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PC1 | — | GPIO | TMS SWDIO |

— | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PC2 | — | GPIO | TDI | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PC3 | — | GPIO | TDO SWO |

— | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PC4 | C1- | GPIO | U7Rx | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S7 |

| PC5 | C1+ | GPIO | U7Tx | — | — | — | — | — | RTCCLK | — | — | — | — | — | — | — | EPI0S6 |

| PC6 | C0+ | GPIO | U5Rx | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S5 |

| PC7 | C0- | GPIO | U5Tx | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S4 |

| PD0 | AIN15 | GPIO | — | I2C7SCL | T0CCP0 | — | C0o | — | — | — | — | — | — | — | — | — | SSI2XDAT1 |

| PD1 | AIN14 | GPIO | — | I2C7SDA | T0CCP1 | — | C1o | — | — | — | — | — | — | — | — | — | SSI2XDAT0 |

| PD2 | AIN13 | GPIO | — | I2C8SCL | T1CCP0 | — | C2o | — | — | — | — | — | — | — | — | — | SSI2Fass |

| PD3 | AIN12 | GPIO | — | I2C8SDA | T1CCP1 | — | — | — | — | — | — | — | — | — | — | — | SSI2Clk |

| PD4 | AIN7 | GPIO | U2Rx | — | T3CCP0 | — | — | — | — | — | — | — | — | — | — | — | SSI1XDAT2 |

| PD5 | AIN6 | GPIO | U2Tx | — | T3CCP1 | — | — | — | — | — | — | — | — | — | — | — | SSI1XDAT3 |

| PD6 | AIN5 | GPIO | U2RTS | — | T4CCP0 | — | USB0EPEN | — | — | — | — | — | — | — | — | — | SSI2XDAT3 |

| PD7 | AIN4 | GPIO | U2CTS | — | T4CCP1 | — | USB0OFLT | — | — | NMI | — | — | — | — | — | — | SSI2XDAT2 |

| PE0 | AIN3 | GPIO | U1RTS | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE1 | AIN2 | GPIO | U1DSR | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE2 | AIN1 | GPIO | U1DCD | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE3 | AIN0 | GPIO | U1DTR | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PE4 | AIN9 | GPIO | U1RI | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI1XDAT0 |

| PE5 | AIN8 | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | — | SSIXDAT1 |

| PF0 | — | GPIO | — | — | — | — | EN0LED0 | M0PWM0 | — | — | — | — | — | — | — | SSI3XDAT1 | TRD2 |

| PF1 | — | GPIO | — | — | — | — | EN0LED2 | M0PWM1 | — | — | — | — | — | — | — | SSI3XDAT0 | TRD1 |

| PF2 | — | GPIO | — | — | — | — | — | M0PWM2 | — | — | — | — | — | — | — | SSI3Fss | TRD0 |

| PF3 | — | GPIO | — | — | — | — | — | M0PWM3 | — | — | — | — | — | — | — | SSI3Clk | TRCLK |

| PF4 | — | GPIO | — | — | — | — | EN0LED1 | M0FAULT0 | — | — | — | — | — | — | — | SSI3XDA2 | TRD3 |

| IO | Analog Function | Digital Function (GPIOx->PCTL PMCn Field Encoding) | |||||||||||||||

| 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF | ||

| 0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 | ||

| PG0 | — | GPIO | — | I2C1SLC | — | — | EN0PPS | M0PWM4 | — | — | — | — | — | — | — | — | EPI0S11 |

| PG1 | — | GPIO | — | I2C1SDA | — | — | — | M0PWM5 | — | — | — | — | — | — | — | — | EPI0S10 |

| PH0 | — | GPIO | U0RTS | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S0 |

| PH1 | — | GPIO | U0CTS | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S1 |

| PH2 | — | GPIO | U0DCD | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S2 |

| PH3 | — | GPIO | U0DSR | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S3 |

| PJ0 | — | GPIO | U3Rx | — | — | — | EN0PPS | — | — | — | — | — | — | — | — | — | — |

| PJ1 | — | GPIO | U3Tx | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PK0 | AIN16 | GPIO | U4Rx | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S0 |

| PK1 | AIN17 | GPIO | U4Tx | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S1 |

| PK2 | AIN18 | GPIO | U4RTS | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S2 |

| PK3 | AIN19 | GPIO | U4CTS | — | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S3 |

| PK4 | — | GPIO | — | I2C3SCL | — | — | EN0LED0 | M0PWM6 | — | — | — | — | — | — | — | — | EPI0S32 |

| PK5 | — | GPIO | — | I2C3SDA | — | — | EN0LED2 | M0PWM7 | — | — | — | — | — | — | — | — | EPI0S31 |

| PK6 | — | GPIO | — | I2C4SCL | — | — | EN0LED1 | M0FAULT1 | — | — | — | — | — | — | — | — | EPI0S25 |

| PK7 | — | GPIO | U0RI | I2C4SDA | — | — | RTCCLK | M0FAULT2 | — | — | — | — | — | — | — | — | EPI0S24 |

| PL0 | — | GPIO | — | I2C2SDA | — | — | — | M0FAULT3 | — | — | — | — | — | — | — | USB0D0 | EPI0S16 |

| PL1 | — | GPIO | — | I2C2SCL | — | — | — | PhA0 | — | — | — | — | — | — | — | USB0D1 | EPI0S17 |

| PL2 | — | GPIO | — | — | — | — | C0o | PhB0 | — | — | — | — | — | — | — | USB0D2 | EPI0S18 |

| PL3 | — | GPIO | — | — | — | — | C1o | IDX0 | — | — | — | — | — | — | — | USB0D3 | EPI0S19 |

| PL4 | — | GPIO | — | — | T0CCP0 | — | — | — | — | — | — | — | — | — | — | USB0D4 | EPI0S26 |

| PL5 | — | GPIO | — | — | T0CCP1 | — | — | — | — | — | — | — | — | — | — | USB0D5 | EPI0S33 |

| PL6 | USB0DP | GPIO | — | — | T1CCP0 | — | — | — | — | — | — | — | — | — | — | — | — |

| PL7 | USB0DM | GPIO | — | — | T1CCP1 | — | — | — | — | — | — | — | — | — | — | — | — |

| PM0 | — | GPIO | — | — | T2CCP0 | — | — | — | — | — | — | — | — | — | — | — | EPI0S15 |

| PM1 | — | GPIO | — | — | T2CCP1 | — | — | — | — | — | — | — | — | — | — | — | EPI0S14 |

| PM2 | — | GPIO | — | — | T3CCP0 | — | — | — | — | — | — | — | — | — | — | — | EPI0S13 |

| PM3 | — | GPIO | — | — | T3CCP1 | — | — | — | — | — | — | — | — | — | — | — | EPI0S12 |

| PM4 | TMPR3 | GPIO | U0CTS | — | T4CCP0 | — | — | — | — | — | — | — | — | — | — | — | — |

| PM5 | TMPR2 | GPIO | U0DCD | — | T4CCP1 | — | — | — | — | — | — | — | — | — | — | — | — |

| PM6 | TMPR1 | GPIO | U0DSR | — | T5CCP0 | — | — | — | — | — | — | — | — | — | — | — | — |

| PM7 | TMPR0 | GPIO | U0RI | — | T5CCP1 | — | — | — | — | — | — | — | — | — | — | — | — |

| PN0 | — | GPIO | U1RTS | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PN1 | — | GPIO | U1CTS | — | — | — | — | — | — | — | — | — | — | — | — | — | — |

| PN2 | — | GPIO | U1DCD | U2RTS | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S29 |

| PN3 | — | GPIO | U1DSR | U2CTS | — | — | — | — | — | — | — | — | — | — | — | — | EPI0S30 |

| PN4 | — | GPIO | U1DTR | U3RTS | I2C2SDA | — | — | — | — | — | — | — | — | — | — | — | EPI0S34 |

| PN5 | — | GPIO | U1RI | U3CTS | I2C2SCL | — | — | — | — | — | — | — | — | — | — | — | EPI0S35 |

| PP0 | C2+ | GPIO | U6Rx | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3XDAT2 |

| PP1 | C2- | GPIO | U6Tx | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3XDAT3 |

| PP2 | — | GPIO | U0DTR | — | — | — | — | — | — | — | — | — | — | — | — | USB0NXT | EPI0S29 |

| PP3 | — | GPIO | U1CTS | U0DCD | — | — | — | — | RTCCLK | — | — | — | — | — | — | USB0DIR | EPI0S30 |

| PP4 | — | GPIO | U3RTS | U0DSR | — | — | — | — | — | — | — | — | — | — | — | USB0D7 | — |

| PP5 | — | GPIO | U3CTS | I2C2SCL | — | — | — | — | — | — | — | — | — | — | — | USB0D6 | — |

| PQ0 | — | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3Clk | EPI0S20 |

| PQ1 | — | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3Fss | EPI0S21 |

| PQ2 | — | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3XDAT0 | EPI0S22 |

| PQ3 | — | GPIO | — | — | — | — | — | — | — | — | — | — | — | — | — | SSI3XDAT1 | EPI0S23 |

| PQ4 | — | GPIO | U1Rx | — | — | — | — | — | DIVSCLK | — | — | — | — | — | — | — | — |

| I/O | Analog Function |

0000 | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

| 0x0 | 0x1 | 0x2 | 0x3 | 0x4 | 0x5 | 0x6 | 0x7 | 0x8 | 0x9 | 0xA | 0xB | 0xC | 0xD | 0xE | 0xF | ||

| Digital Function (GPIOx->PCTL PMCn Field Encoding) | |||||||||||||||||

PD7 and PE7 are configured as GPIO by default but is locked and can only be reprogrammed by unlocking the pin in the GPIOLOCK register and uncommitting it by setting the GPIOCR register.